Adalah suatu rangkaian yang dapat menyimpan state biner (sepanjang masih terdapat power pada rangkaian) sampai terjadi perubahan pada sinyal inputnya rangkaian dasar flip-flop. Flip-flop dapat dibuat dari dua buah gerbang NAND atau NOR berikut ini:

![clip_image002[8] clip_image002[8]](https://www.tneutron.net/elektro/wp-content/uploads/sites/2/2017/05/clip_image0028_thumb.jpg)

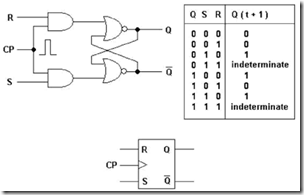

A. RS Flip-Flop Dengan Clock

Dengan menambah beberapa gerbang pada bagian input rangkaian dasar, flip-flop tersebut hanya dapat merespon input selama terdapat clock pulsa. Output dari flip-flop tidak akan berubah selama clock pulsanya 0 meskipun terjadi perubahan pada inputnya. Output flip-flop hanya akan berubah sesuai dengan perubahan inputnya jika clock pulsa bernilai 1.

B. D Flip-Flop

D flip-flop merupakan modifikasi dari RS flip-flop memakai clock. Input D disalurkan secara langsung ke S.

![clip_image008[7] clip_image008[7]](https://www.tneutron.net/elektro/wp-content/uploads/sites/2/2017/05/clip_image0087_thumb.jpg)

C. JK Flip-Flop

State-state yang tidak didefinisikan pada RS flip-flop, pada JK flip-flop ini state tersebut didefinisikan. Jika pada RS flip-flop kondisi R dan S sama dengan 1, maka kondisi seperti ini tidak didefinisikan, maka pada JK flip-flop jika kondisi J dan K sama dengan 1 maka output JK flip-flop tersebut adalah komplemen dari output sebelumnya. Dalam hal ini J setara dengan S dan K setara dengan R. untuk lebih jelasnya kita perhatikan diagram dibawah ini.

![clip_image013[7] clip_image013[7]](https://www.tneutron.net/elektro/wp-content/uploads/sites/2/2017/05/clip_image0137_thumb.jpg)

D. T Flip-Flop

Adalah versi JK flip-flop dengan single input.T flip-flop mempunyai kemampuan yaitu membuat toggle seperti pada tabel dibawah ini.

![clip_image015[7] clip_image015[7]](https://www.tneutron.net/elektro/wp-content/uploads/sites/2/2017/05/clip_image0157_thumb.jpg)

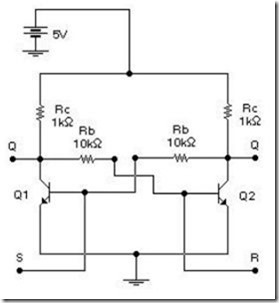

Rangkaian flip- flop yang dibentuk dari komponen diskrit

Diagram flip -flop yang menggunakan komponen diskrit, yaiturangkaian yang dibentuk dari 2 buah transistor bipolar Q1 dan Q2, dua buah resistor kolektor R C, dan dua buah resistor base R b seperti pada Gambar. Pada dasarnya rangkaian flip -flop ini terdiri dari dua buah 2penguat inversi yang dihubungkan saling silang, keluaran penguat yangsatu dihubungkan dengan masukan yang lain, dan sebaliknya.

Rangkaian flip-flopdari komponen diskrit

Gambar diatas adalah rangkaian yang terbentuk dari dua transistorbipolar dan empat resistor yang menunjukkan rangkaian saling silang.Dengan memberi sinyal positif pada base (S), transistor Q1 on jenuh, tegangan kolekor Q1 rendah (antara 0,2 sampai 0,4 V), tegangan yang rendah ini, melalui resistor Rb mengikat base transitor Q 2 menjadi keadaan off, mengakibatkan tegangan kolektor Q2 naik mendekatisumber Vcc (tinggi), selanjutnya tegangan ini akan mengancing base Q1 tetap tinggi sehingga keluaran Q1 tetap rendah. Dengan demikian terjadi kestabilan pada keadaan keluaran Q1 rendah, dan keluaran Q2 tinggi. Keadaan ini akan tetap demikian.